当前位置:操作系统 > 电脑通通透 >>

答案:作为DDR的易做图人,DDR-Ⅱ在规范制定之初就引起了广泛的关注,进入2002年,三星、Elpida、Hynix、Micron等都相继发布了DDR-Ⅱ芯片(最早由三星在5月28日发布),让人觉得DDR-Ⅱ突然和我们近了。可是,DDR-Ⅱ规范却一直没有正式公开,在JEDEC上仍只有一篇ATi技术人员写的,在目前看来有些内容都已过时的简要介绍。

原来,DDR-Ⅱ标准到2002年10月完成度也没有达到100%(厂商透露大约为95%),而上述厂商所推出的芯片也在不断的修改中,预计正式的规范将在明年第一季度推出。不过,DDR-Ⅱ的主体设计已经完成,不会有大的改动,所以通过这些“试验性”芯片,我们仍可掌握DDR-Ⅱ的主要信息。

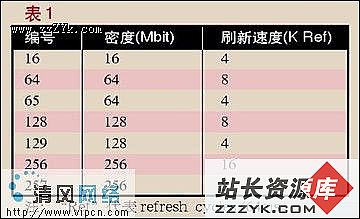

DDR-Ⅱ相对于DDR 的主要改进如下:

DDR-Ⅱ与目前的DDR对比表

由于DDR-Ⅱ相对DDR-I的设计变动并不大,因此很多操作就不在此详细介绍了,本文重点阐述DDR-Ⅱ的一些重要变化。

一、 DDR-Ⅱ内存结构

DDR-Ⅱ内存的预取设计是4bit,通过DDR的讲述,大家现在应该知道是什么意思了吧。

上文已经说过,SDRAM有两个时钟,一个是内部时钟,一个是外部时钟。在SDRAM与DDR时代,这两个时钟频率是相同的,但在DDR-Ⅱ内存中,内部时钟变成了外部时钟的一半。以DDR-Ⅱ 400为例,数据传输频率为400MHz(对于每个数据引脚,则是400Mbps/pin),外部时钟频率为200MHz,内部时钟频率为100MHz。因为内部一次传输的数据就可供外部接口传输4次,虽然以DDR方式传输,但数据传输频率的基准——外部时钟频率仍要是内部时钟的两倍才行。就如RDRAM PC800一样,其内部时钟频率也为100MHz,是传输频率的1/8。

DDR-Ⅱ、DDR与SDRAM的操作时钟比较

所以,当预取容量超过接口一次DDR的传输量时,内部时钟必须降低(除非数据传输不是DDR方式,而是一个时钟周期4次)。如果内部时钟也达到200MHz,那外部时钟也要达到400MHz,这会使成本有大幅度提高。因此,DDR-Ⅱ虽然实现了4-bit预取,但在实际效能上,与DDR是一样的。在上面那幅比较图中,可以看出厂商们的一种误导,它虽然表示出在相同的核心频率下,DDR-Ⅱ达到了两倍于DDR的的带宽,但前提是DDR-Ⅱ的外部时钟频率也是DDR和SDRAM的两倍。在DDR的时钟频率已经达到166/200MHz的今天,再用100MHz去比较,显然意义不大。这点也请大家们注意识别,上图更多的是说明DDR-Ⅱ内外时钟的差异。毕竟内部时钟由外部决定,所以外部时钟才是比较的根本基准。

总之,现在大家要明确认识,在外部时钟频率相同的情况下,DDR-Ⅱ与DDR的带宽一样。

二、 DDR-Ⅱ的新操作与新时序设计

1、片外驱动调校(OCD,Off-Chip Driver)

DDR-Ⅱ内存在开机时也会有初始化过程,同时在EMRS中加入了新设置选项,由于大同小异,在此就不多说了。在EMRS阶段,DDR-Ⅱ加入了可选的OCD功能。OCD的主要用意在于调整I/O接口端的电压,来补偿上拉与下拉电阻值。目的是让DQS与DQ数据信号之间的偏差降低到最小。调校期间,分别测试DQS高电平/DQ高电平,与DQS低电平/DQ高电平时的同步情况,如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测试合格才退出OCD操作。

OCD的作用在于调整DQS与DQ之间的同步,以确保信号的完整与可靠性

不过,据一些厂商的技术人员介绍,一般情况下有DQS#(差分DQS时)就基本可以保证同步的准确性,而且OCD的调整对其他操作也有一定影响,因此在普通台式机上不需要用OCD功能,它一般只会出现在高端产品中,如对数据完整性非常敏感的服务器等。

[page_break] 2、片内终结(ODT,On-Die Termination)

所谓的终结,就是让信号被电路的终端被吸收掉,而不会在电路上形成反射,造成对后面信号的影响。在DDR时代,控制与数据信号的终结在主板上完成,每块DDR主板在DIMM槽的旁边都会有一个终结电压岛的设计,它主要由一排终结电阻构成。长期以来,这个电压岛一直是DDR主板设计上的一个难点。而ODT的出现,则将这个难点消灭了。

顾名思义,ODT就是将终结电阻移植到了芯片内部,主板上不在有终结电路。ODT的功能与禁止由北桥芯片控制,ODT所终结的信号包括DQS、RDQS(为8bit位宽芯片增设的专用DQS读取信号,主要用来简化一个模组中同时使用4与8bit位宽芯片时的控制设计)、DQ、DM等。需要不需要该芯片进行终结由北桥控制。 那么具体的终结操作如果实现呢?首先要确定系统中有几条模组,并因此来决定终结的等效电阻值,有150和75Ω两档,这一切由北桥在开机进行EMRS时进行设置。

在向内存写入时,如果只有一条DIMM,那么这条DIMM就自己进行终结,终结电阻等效为150Ω。如果为两条DIMM,一条工作时,另一条负责终结,但等效电阻为75Ω

在从内存读出时,终结操作也将在北桥内进行,如果有两条DIMM,不工作的那一条将会终结信号在另一方向的余波,等效电阻也因DIMM的数量而有两种设置

两个DIMM在交错工作中的ODT情况,第一个模组工作时,第二个模组进行终结操作,等第二个模组工作时,第一个模组进行终结操作(上图可点击放大)

现在我们应该基本了解了ODT的功能,它在很大程度上减少了内存芯片在读取时的I/O功率消耗,并简化了主板的设计,降低了主板成本。而且ODT也要比主板终结更及时有效,从而也成为了提高信号质量的重要功能,这有助于降低日后DDR-Ⅱ进一步提速的难度。但是,由于为了确保信号的有效终结,终结操作期将会比数据传输期稍长,从而多占用一个时钟周期的时间而造成总线空闲。不过,有些厂商的技术人员称,通过精确设置tDQSS,可以避免出现总线空闲。(出处:http://www.zzzyk.com/)

| 上一页 [1] [2] |