Allegro平台能运行于Linux

Cadence设计系统公司将发布一个名为Allegro的平台,它可以为整个系统中从IC到封装、从封装到印刷电路板的高速互连建模。Allegro囊括了Cadence已有的PCB和封装工具,并增加了2种新的封装工具。此外,它允许不同的芯片、封装和PCB设计小组使用同一个系统互连模型进行工作。该平台的用户将能够跟踪一个信号,自它从IC的I/O缓冲器通过再分配层开始,直至穿过裸片的突起焊盘、封装基底、连接器到达PCB。“Allegro平台提供了设计这些互连所需的全部技术,并支持完成这种任务所需的方法学。”Cadence公司硅-封装-电路板业务部战略行销副总裁Jamie Metcalfe表示。

今天,不同的设计小组在工作时往往彼此分隔。这些小组通常从系统架构师那里收到电子表格式的草案规范,然后埋头设计各自的系统互连部分,Metcalfe说。

目前为止,业界还没有可行的技术允许架构师对贯穿所有结构的互连进行建模,并允许不同的互连设计师相互交流,以便通过权衡作出最佳选择。Cadence的早期工具允许封装和PCB设计师监视从电路板到封装的信号完整性和时序问题,但他们不能设计和分析从IC到封装的互连。Allegro的出现改变了这种状况。

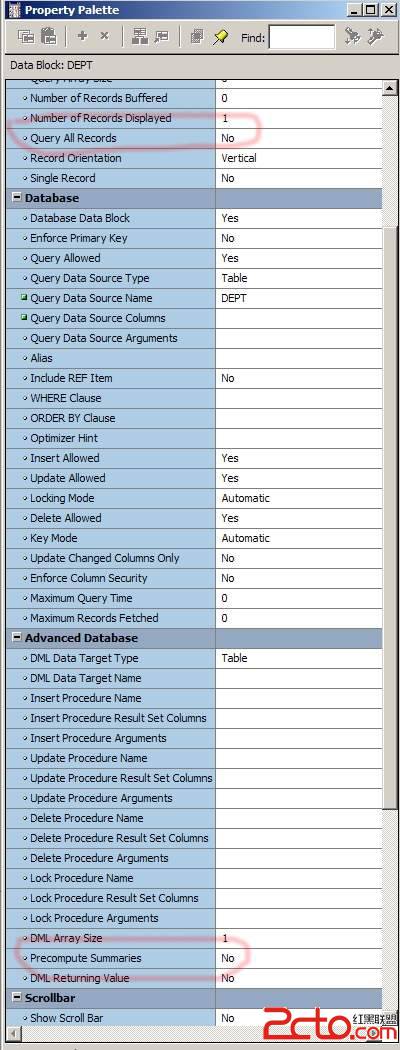

目前已可对外授权的2种工具是Allegro Package Designer和Allegro Package SI。系统架构师可以利用Package Designer创建一种新类型的模型,它描述了贯穿整个流程的互连。

这种虚拟系统互连(VSIC)模型将捕捉设计团队在系统互连或粗略版图方面的意图,然后该模型被传递给电路设计师、封装设计师和PCB设计师,每类设计师在顾及整个互连的条件下实现系统的某一部分。

VSIC模型通常包含对I/O缓冲器的行为描述和约束拓扑。“例如,我们可以插入一个拓扑,告诉系统一个特殊的互连必须以差分对的形式实现,而且必须在24英寸的FR-4材料上工作,并以某种特殊方式终止。”Metcalfe说。

VSIC模型还包含适用于信号关键段的底层规划指南。“设计师可以在实现各自部分的设计或仿真缓冲器和互连的行为时将这些指南作为约束条件使用。”Metcalfe表示。

在这种方法学下,I/O缓冲器设计师可以使用Cadence的Virtuoso工具。此外,设计师可以使用Allegro Package Designer和Allegro Package SI设计突起阵列,用Allegro Packaging工具设计封装,用Allegro PCB工具设计电路板。设计小组在设计各自的互连部分时都可以参考VSIC模型,并继续完善此模型。不过,模型的任何部分都可以被“锁定”以防止改动,Metcalfe补充道。

“Beta测试表明,使用Allegro平台及其方法学可以使系统设计周期缩短8到12周,”Metcalfe宣称,“Allegro还能削减高达66%的封装成本。”该平台和方法学可以支持专用芯片设计套件的插件。

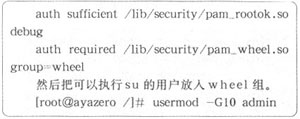

Allegro平台能运行于Windows、Sun Solaris、HP-UX、IBM AIX和Red Hat Linux。Allegro Package Designer和Package SI的一年许可证费用起价分别为5.4万和4.5万美元。与Allegro PCB SI一起使用的PCI Express芯片设计套件可以从www.allegroSI.com免费下载。